Ex. 2: Logic synthesis, P&R and netlist simulation

Group: rvlab01

Small changes top the rlight_module where applied to make it synthesizable. Changed a pattern-applied-flag between processes from a shared flag bit to a unidirectional signaling line.

Warnings regarding student_rlight?

Files in rvlab/build/rvlab_fpga_top/syn:rvlab/build/rvlab_fpga_top/syn**rvlab/build/rvlab_fpga_top/syn result.json: List of all reports

rvlab_fpga_top.drc.txt: Design rule check (short overview with count of violations)

rvlab_fpga_top.methodology.txt: Special form of DRC (https://support.xilinx.com/s/article/1173821?language=en_US)

rvlab_fpga_top.timing_summary.txt

vivado.log

rvlab_fpga_top.dcp: Archive containing a design checkpoint

rvlab_fpga_top.funcsim.v: Generated stuff for functional simulation

rvlab_fpga_top.qor_assessment.txt: Quality of realization score Assessment Score

Prediction (Table from https://support.xilinx.com/s/article/1110761?language=en_US)

#1 Design will not complete implementation

#2 Design will complete implementation but will not achieve timing goals

#3 Design runs have a small chance of success

#4 Design should achieve goals if run with a few directives #5 Design will easily meet timing

rvlab_fpga_top.qor_assessment.txt shows that our design reached a score of 5 meaning that all timing requirements are meet rvlab_fpga_top.utilization.txt: Utilization of hardware blocks

1. Questions

1. Which files contain the definition of the TL-UL and board level (DDR3, LED, …) connections ?

The relationship between TL-UL signals and physical connections on the board level are described in the .xdc constraint file.

2. What is the maximum operating speed in Megahertz of the main clk “clk” after the Place & Route ?

The maximum frequency for sys_clk (clk) can be found by analyzing rvlab_fpga_top.timming_summary.txt. According to the Max Delay Paths analysis for sys_clk the worst slack is 6.567ns with a clock period of 20ns.

The maximum frequency can be calculated to be 1/(20ns-6.567ns) (approx. 74.4Mhz). Higher clockspeeds would require a different optimization of the place and route process and/or design changes.

3. Name the three most important differences between functional simulation of the HDL and netlist simulation.

Functional simulation is used to validate the logical function of a HDL code, which may not necessarily be synthesizable, while a netlist simulation is performed after synthesis to check and debug the implementation. There are no propagation delays, setup times etc. modeled in a function simulation while a netlist simulation takes those parameters into account which can be used to find timing problems or violations in the design. Functional simulation is usually faster and less compuationally complex then a netlist simulation

2. Deliverables of task 3

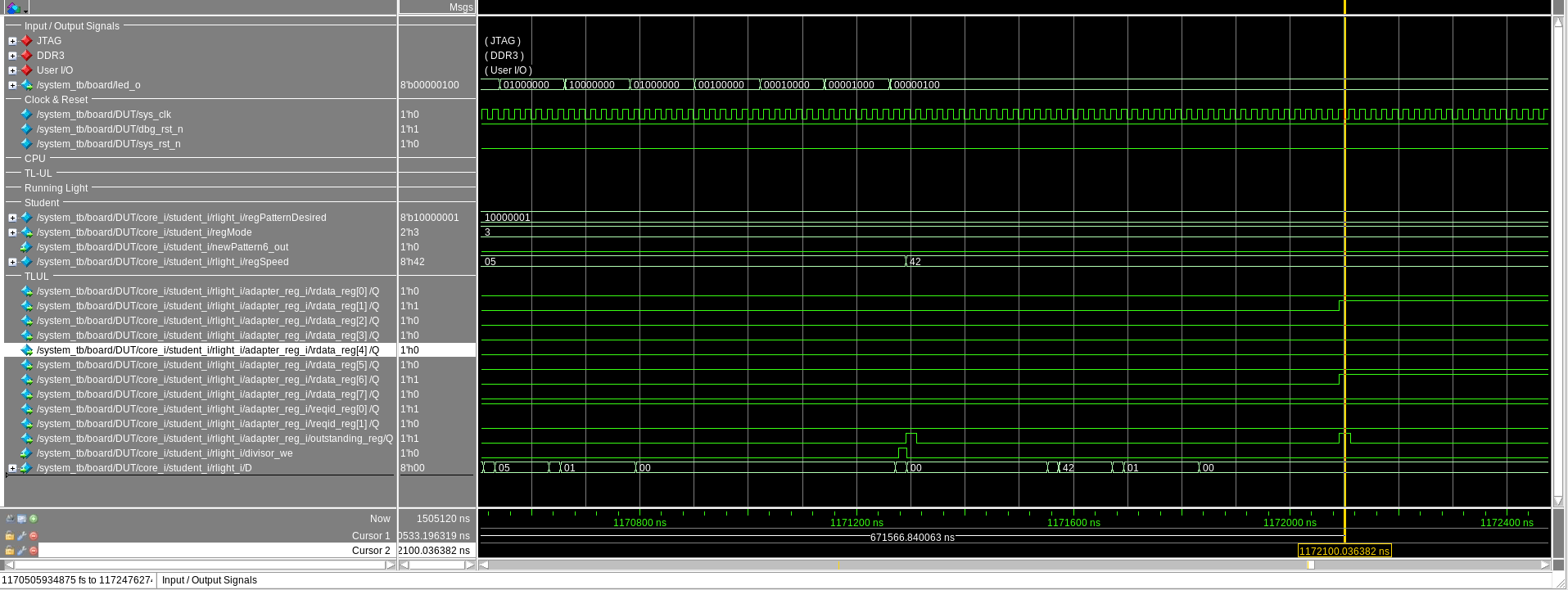

1. While the running light is running with a pause time of 5 cycles: A write access (writing 0x42) to the delay register followed by a read access.

The duration of 5 cycle per pattern step can be seen in the wave of the led_o signal on the following screenshot. After writing the 0x42 to the delay register (regSpeed) the pattern changes outside of the shown timeframe. Due to the lack of the re-signal we can only infere the read access time by the outstanding_reg.

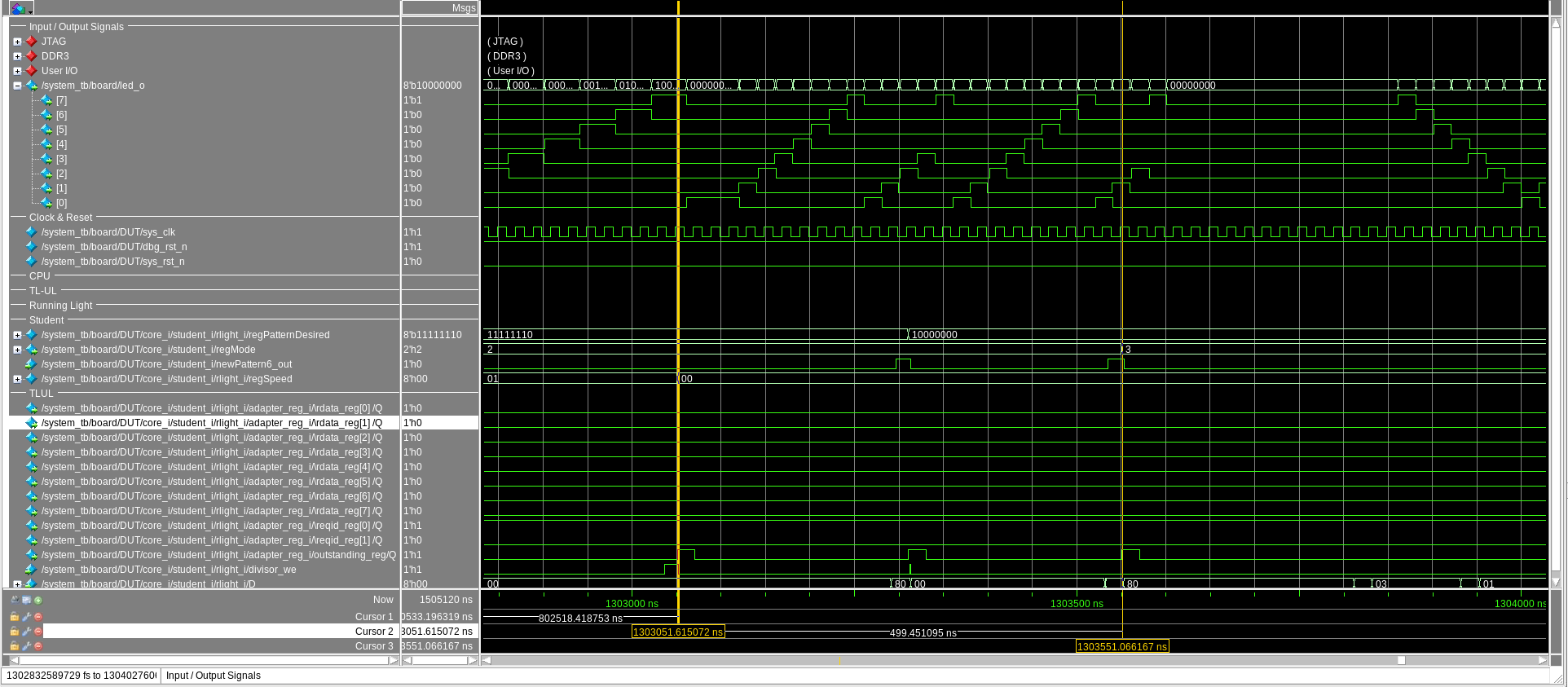

2. Two complete cycles with the following configurations: #. mode=right, initial pattern=11111110, pause = 1 cycle #. mode=ping-pong, initial pattern=10000000, pause = 0 cycles (i.e. the pattern changes every clock cycle)

The following mode demonstrates the switching of the pattern, speed and animation mode.

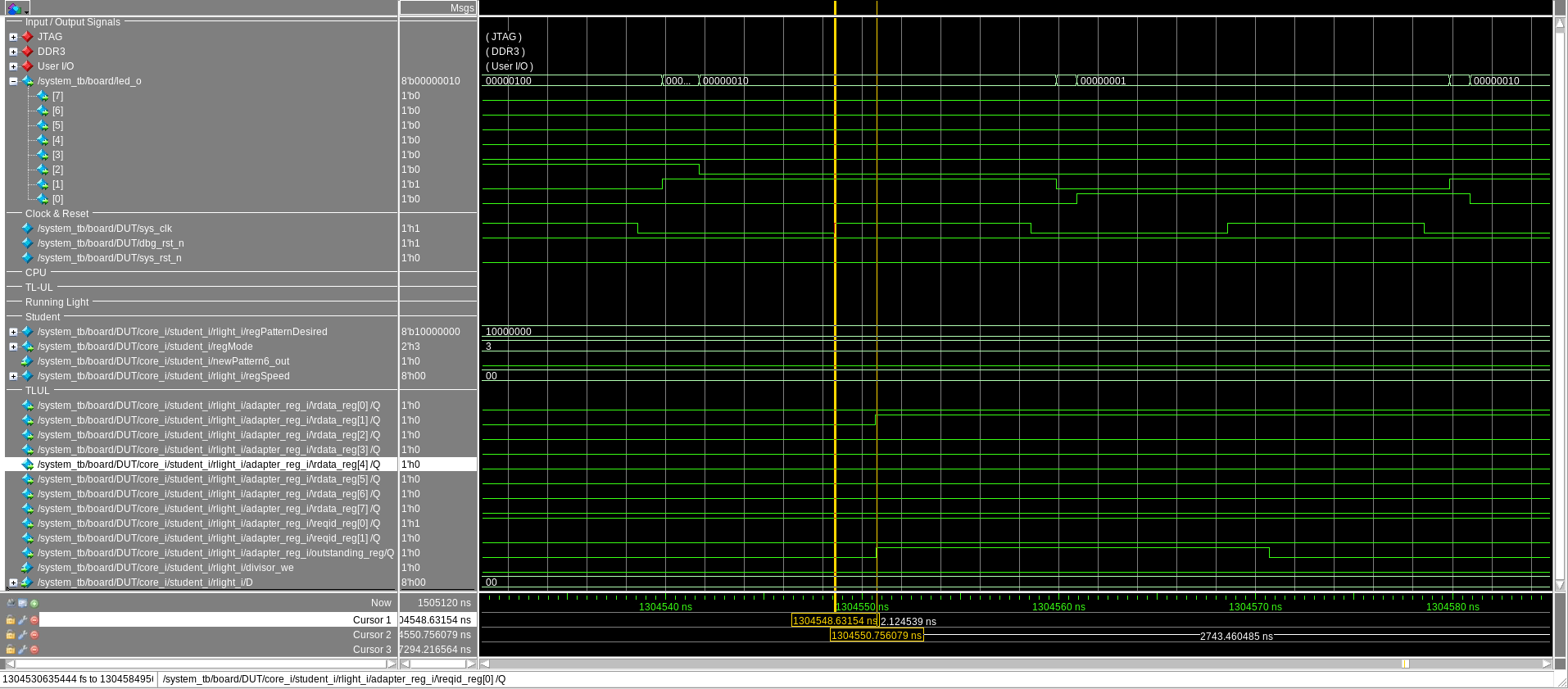

3. A read access to the pattern register which clearly shows the delayed arrival of the data at register bus after the rising clock edge.

In the following screenshot we can observe the delay (approx. 2ns) of the read register (rdata) becoming stable after the rising edge of the sys_clk. The rdata register then hold the current pattern state.

Appendix:

main.c: Testbench

running_light_ctrl.c: Rlight module Appendix

running_light_control.h

student_rlight.sv: Slightly modified rlight_module